## **Bias-Stress-Induced Charge Trapping in Organic Thin-Film Transistors**

Boseok Kang<sup>1</sup>, Byungho Moon<sup>1</sup>, Hyun Ho Choi<sup>1</sup> and Kilwon Cho<sup>1</sup>

Dept. of Chemical Engineering, Pohang University of Science and Technology, Pohang 790-784, Korea

Tel.: 82-54-279-2270, E-mail: kwcho@postech.ac.kr

Organic thin-film transistors (OTFTs) have received considerable attention as switching elements for flexible displays on plastic substrates. However, although OTFTs have been developed with device performances superior to those of hydrogenated amorphous silicon (a-Si:H) TFTs,<sup>[1]</sup> the electrical stability of OTFTs (called bias-stress stability) remains a critical obstacle to the commercialization of these devices. Hole/electron trapping in the gate dielectric, organic semiconductors, and interfaces is the main reason for the bias-stress stability.<sup>[2]</sup>

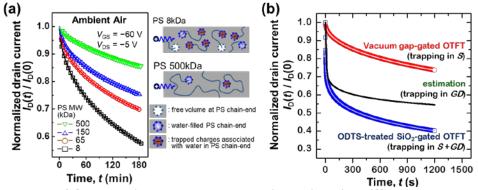

Here, we investigated the effect of the molecular weight (MW) of a polystyrene (PS) gate dielectric on the bias stability of the OTFTs (Fig. 1a). Pentacene TFTs were prepared using different PS dielectrics with MWs ranging from 8 to 500 kDa. The field-effect mobilities of the TFTs and morphology of the pentacene did not vary significantly with MW. However, the  $I_D$  decay was highly dependent on the PS MW under an ON-bias stress ( $V_{GS} = -60 \text{ V}$ ,  $V_{DS} = -5 \text{ V}$ ) in ambient air, whereas the  $I_D$  decay was independent of MW under vacuum condition. Such difference was attributed to different degrees of water vapor absorption at the PS dielectrics.

Furthermore, we sought to decouple the two contributions to bias-induced charge trapping, *i.e.* charge trapping at the semiconductor side of the interface and the dielectric side of the interface. Two separate OTFTs that shared a common semiconductor were prepared and independently operated with SiO<sub>2</sub> and vacuum gap dielectrics, respectively.<sup>[4]</sup> In the OTFT with a vacuum-gap dielectric, only the semiconductor side of the interface contributed to charge trapping. Therefore, the contribution from the dielectric side of the interface to charge trapping can be extracted from the bias-stability results for the devices with SiO<sub>2</sub> dielectrics by using a suggested double stretched-exponential formula (Fig. 1b).

Fig. 1. (a)  $I_{\rm D}$  decays of OTFTs using polystyrene gate dielectrics with different MWs and schematic diagrams representing the possible mechanism of the MW-dependent bias stability. (b)  $I_{\rm D}$  decays of OTFTs with SiO<sub>2</sub> and vacuum gap dielectrics and an estimated curve by using the double stretched-exponential formula. Reproduced with permission from Ref [3, 4]. Copyright 2012 2013 Wiley.

We believe that our detailed analysis for the charge-trapping mechanisms in OTFTs will reveal the origins of the bias-stress instabilities observed in these devices, and that future endeavors to reduce such instabilities will enable practical applications of OTFTs in flexible flat panel displays.

## Acknowledgment

This work was supported by a grant (Code No. 2011–0031628) from the Center for Advanced Soft Electronics under the Global Frontier Research Program of the Ministry of Science, ICT and Future Planning, Korea.

## References

- 1. B. Kang, W. H. Lee, K. Cho, ACS Appl. Mater. Intefaces, 5, 2302 (2013).

- 2. W. H. Lee, H. H. Choi, D. H. Kim, K. Cho, Adv. Mater., 26, 1660 (2014).

- 3. H. H. Choi, W. H. Lee, K. Cho, Adv. Funct. Mater., 22, 4833 (2012).

- 4. H. H. Choi, M. S. Kang, M. Kim, H. Kim, J. H. Cho, K. Cho, Adv. Funct. Mater., 23, 690 (2013).